随着新能源汽车、自动驾驶、消费电子、安防等市场的巨大增长,2022年全球影像传感器CIS芯片市场销售规模预计将增长7%,达到219亿美元,未来随着计算摄像、AI技术的不断进步,这一市场将会继续爆发。与常规半导体产业链相同,CMOS传感器CIS芯片制造产业链主要分为设计、代工和封装测试三个环节,峻茂CMOS传感器芯片胶就应用于此。图像传感器芯片是影像系统中的最核心部分,对摄像的品质起到具足轻重的作用,CIS的封装工艺是整个光学领域技术门槛最高的环节,CIS环节也占据整个摄像头产业链一半以上的价值量。

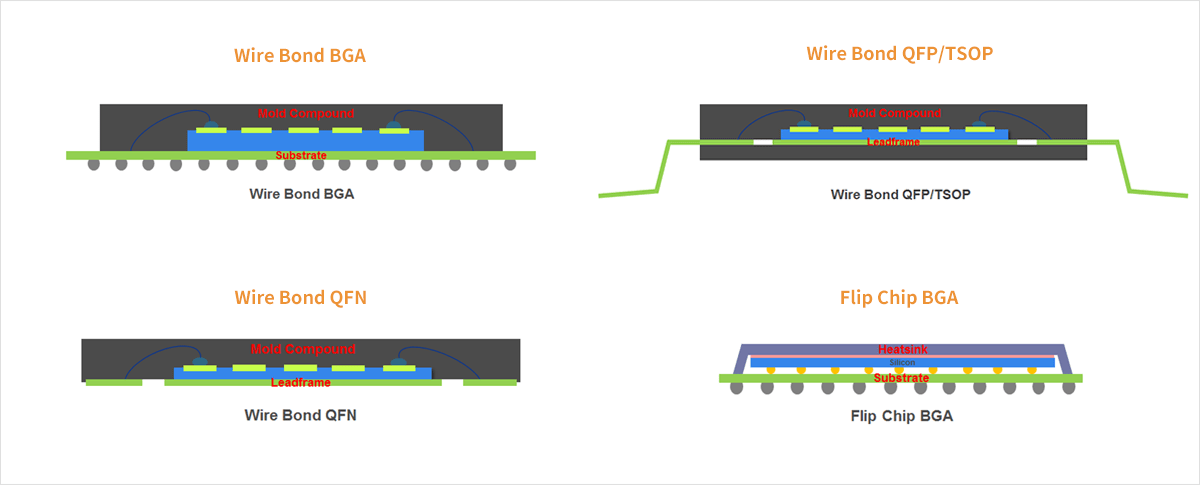

峻茂的CMOS传感器芯片胶可替代进口类产品,能满足车规级、消费电子级测试要求,包括且不限于:耐高低温(-55-280℃)、可抗多次回流焊制程、抗双85测试、耐冷热循环……目前,主流的图像传感器芯片封装工艺包括:芯片级封装(chipscalepackage,csp)、板上集成封装(chiponboard,cob)及倒装芯片封装(flipchip,fc)。

ciscsp是一种目前普遍应用在中低端、低像素(2m像素或以下)图像传感器的waferlevel(晶圆级)封装技术。该封装技术使用晶圆级玻璃与晶圆邦定并在晶圆的图像传感器芯片之间使用围堰隔开,然后在研磨后的晶圆的焊盘区域通过制作焊盘表面或焊盘面内孔侧面环金属连接的硅穿孔技术(tsv:throughsiliconvia)或切割后焊盘侧面的t型金属接触芯片尺寸封装技术,并在晶圆背面延伸线路后制作焊球栅阵列(bga:ballgridarray),然后切割后形成单个密封空腔的图像传感器单元。后端通过smt的方法形成模块组装结构。但是,csp封装具有如下明显的问题:1影响产品性能:厚的支撑玻璃对光的吸收、折射、反射及散射对图像传感器尤其是小像素尺寸产品的性能具有很大的影响;2可靠性问题:封装结构中的构件之间的热膨胀系数差异及空腔内密封气体在后面的smt工艺或产品使用环境的变化中出现可靠性问题;3投资规模大、环境污染控制要求大,生产周期较长,单位芯片成本较高尤其对于高像素大尺寸图像传感器产品;

ciscob封装是一种目前普遍应用在高端、高像素产品(5m像素或以上)图像传感器的dielevel(芯片级)封装技术。该封装技术把经研磨切割后的芯片背面邦定在pcb板的焊盘上使用键合金属导线,装上具有ir玻璃片的支架和镜头,形成组装模块结构。但是,cob封装如下明显的问题:1、微尘控制非常困难,需要超高的洁净室等级,制造维持成本高;2、产品设计定制化、周期长、灵活度不够;3不容易规模化生产;

cisfc封装是一种相对高端、高像素(5m像素或以上)图像传感器的dielevel(芯片级)封装技术。该封装技术把在焊盘做好金素凸块经研磨切割的芯片焊盘直接与pcb的焊盘通过热超声的作用一次性所有接触凸块与焊盘进行连接,形成封装结构。后端通过pcb外侧的焊盘或锡球采用smt的方法形成模块组装结构。但是,fc封装如下明显的问题:1该封装对pcb基板要求很高,与si具有相近的热膨胀系数,成本很高;2制造可靠性难度很大,热超声所有凸块与焊盘连接的一致性要求非常高,凸块与焊盘硬连接,延展性不好;3微尘控制难度大、工艺环境要求高,成本很高。

半导体先进封装工艺复杂程度决定着其对辅料耗材有着严苛的标准和要求,一次失误或疏忽将可能造成难以估量的损失,这就需要其厂商具备跟得上(技术)、稳得住(品控)的能力,除了芯片封装制程用胶外,峻茂在光学领域的用胶还有低温固化、光固化、常温快干等胶水,可用于镜头镜片、模组元器件的粘接固定密封遮光填充等。