引言

本文比较了介质刻蚀的不同方面。讨论了刻蚀电介质的两种主要技术,即二极管RIE和基于高密度的工艺。在这篇论文中,我们将更新这些技术的最新结果,并关注介电膜纳米尺度蚀刻的日益增长的重要性。

装备

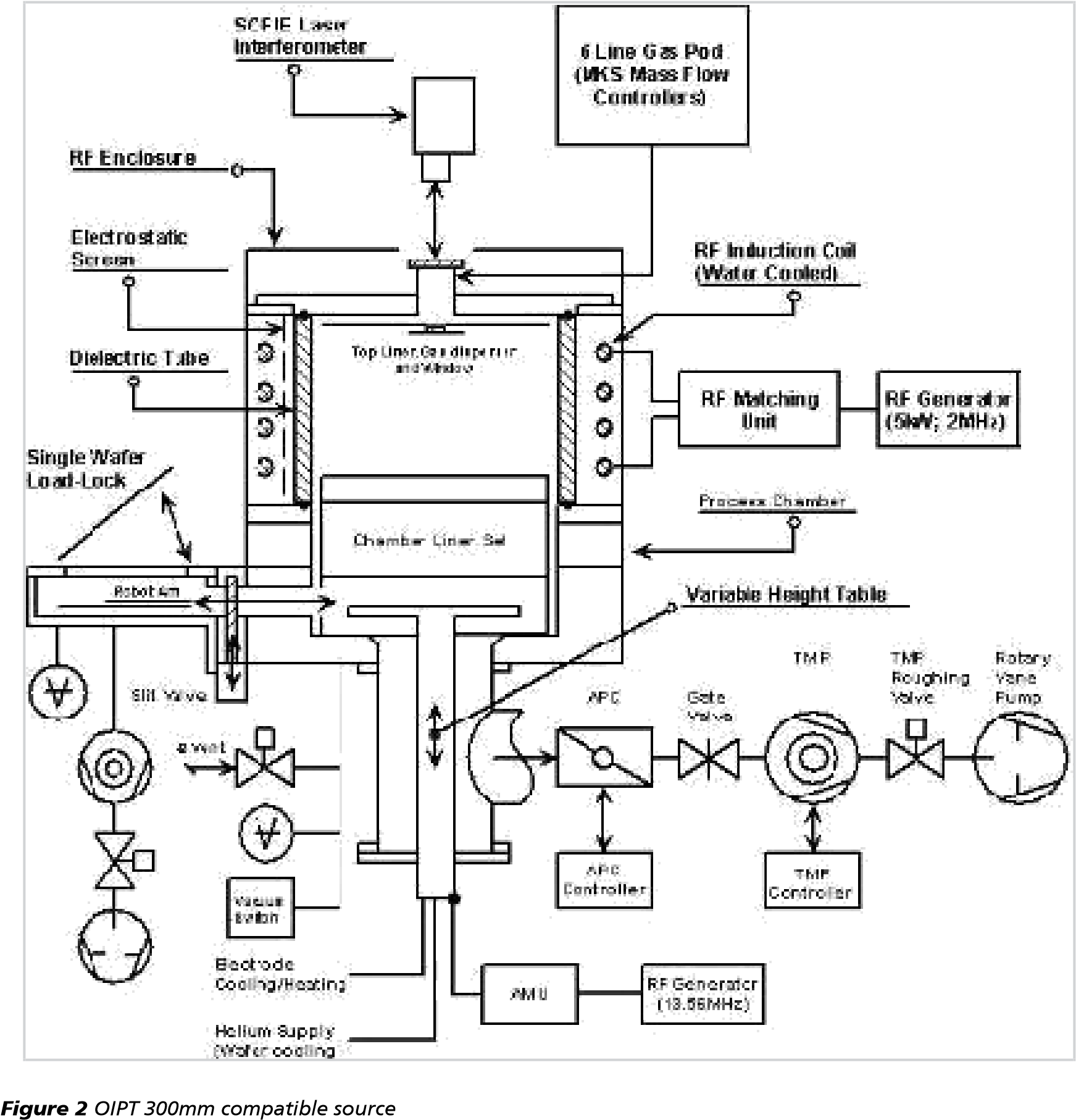

传统的二极管或平行板等离子体室在工业上已经很成熟。平行板系统通常分为两种不同的类型;这些被称为反应离子蚀刻(RIE)或等离子蚀刻(PE)系统。在这两个平行板反应器中,RIE型系统是典型地用于蚀刻介电膜的系统。高密度等离子体(HDP)室被设计成使得等离子体电子在平行于室边界的方向上被激发。最常见的HDP源是OIPT使用的电感耦合等离子体室。在该系统中,等离子体由缠绕在电介质壁外的线圈建立的磁势驱动(典型设计见图2)。

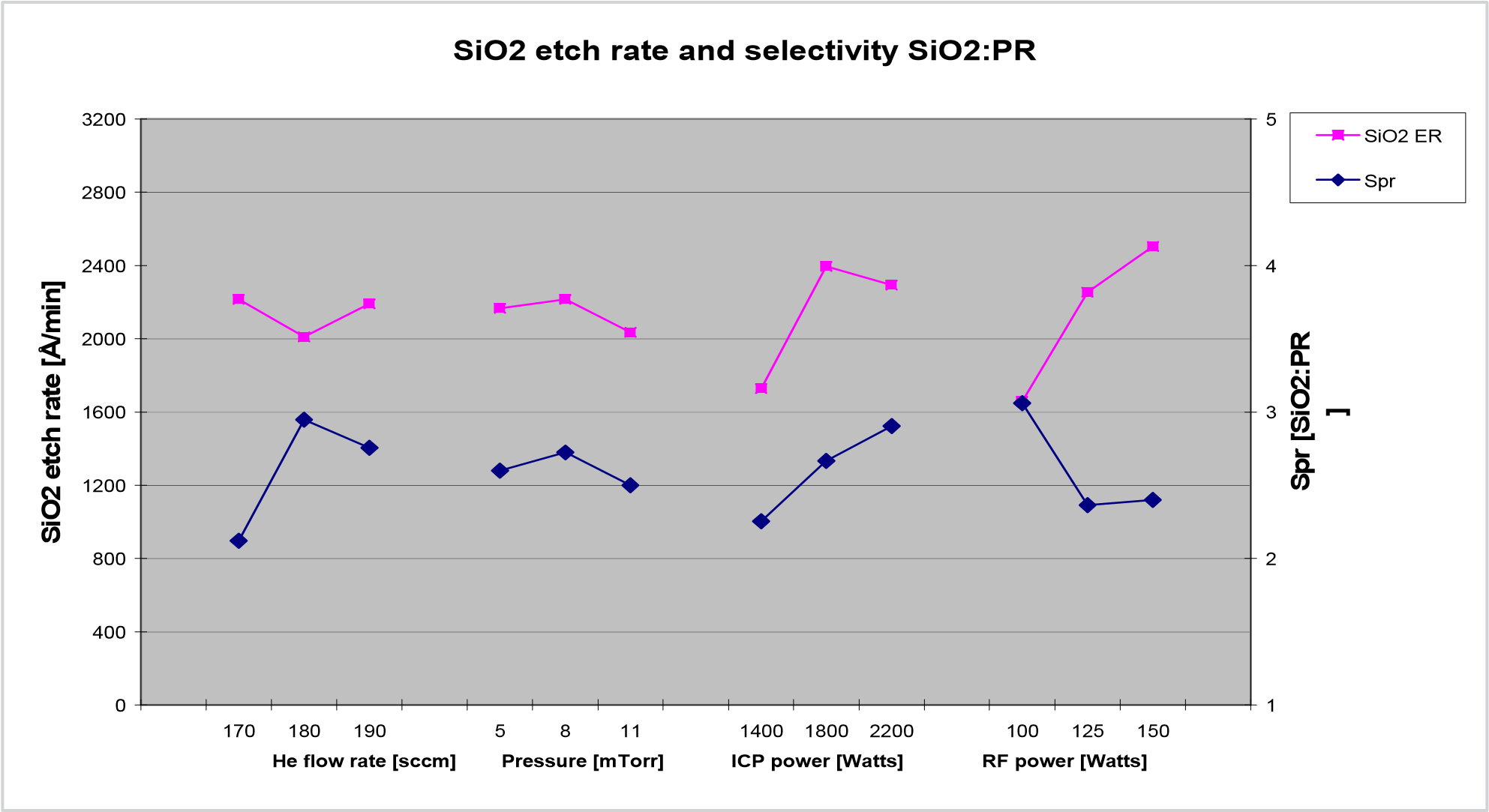

电感耦合等离子体用于电介质蚀刻的主要加工优势是更好的临界尺寸控制、更高的蚀刻速率、更高的纵横比和改进的加工窗口。电介质,特别是二氧化硅的图案化是现代半导体器件、光波导、射频识别、纳米压印等制造中固有的。由于较高的结合能,电介质蚀刻需要侵蚀性的、离子增强的、基于氟的等离子体化学系统。垂直轮廓通过侧壁钝化来实现,通常通过将含碳氟物质引入等离子体(例如,。CF4,CHF3,C4F8)。需要高离子轰击能量来从氧化物中去除聚合物层,以及将活性物质混合到氧化物表面以形成SiFx产物。电介质蚀刻应用通常依赖于聚合物沉积和反应离子蚀刻的竞争影响来实现垂直轮廓,以及在下层上的蚀刻停止。

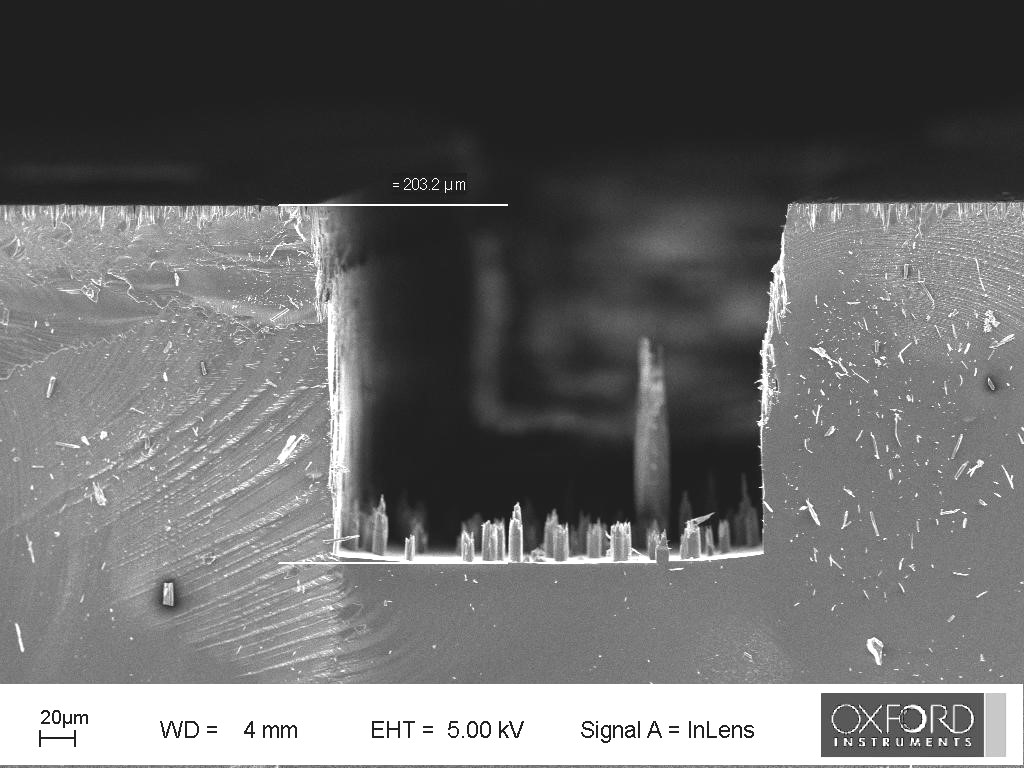

最近的发展表明,需要更深的介电蚀刻,大约> 100 μm。普通的光致抗蚀剂掩模不能用来蚀刻到这个深度,所以使用金属掩模,如铬和镍,其选择性大于100:1.这在可以使用的过程化学中提供了更多的自由度,但是离子通量的控制仍然是最重要的。太高,在达到期望的深度之前,掩模将由于溅射而被侵蚀。扫描电镜图8和9显示了使用铬掩模的深石英蚀刻。对于SEM9,有一个留下残留物的掩蔽问题,但它显示出蚀刻到相当深度的能力。

结论

本文所讨论的用于电介质蚀刻的二极管和电感耦合等离子体工艺在硬件和工艺方面经过了多年的发展。基于电感耦合等离子体的工艺提供了更高的蚀刻速率,具有更好的临界尺寸和各向异性控制,以及更高的纵横比等。实现这些改进需要使用更大的涡轮分子泵,这是有代价的,但是更高的速率的优势远远弥补了这一点。此外,通过利用这些更大的泵和独立的离子流量控制,蚀刻纳米级特征的可能性被打开。

二极管系统确实为蚀刻具有较大线宽的电介质提供了一种成本有效的解决方案,但速度要慢得多,并且不能用于蚀刻纳米级特征。